I do have signals for saturation and overflow that I am going to implement later on but they aren't really used at the moment so don't worry about them.

Serial adder vhdl code how to#

I've been trying to solve this problem for a few hours now and can't seem to figure out how to do it, so could you please take a look and see what I can do to fix it? Would be very much appreciated!

Serial adder vhdl code serial#

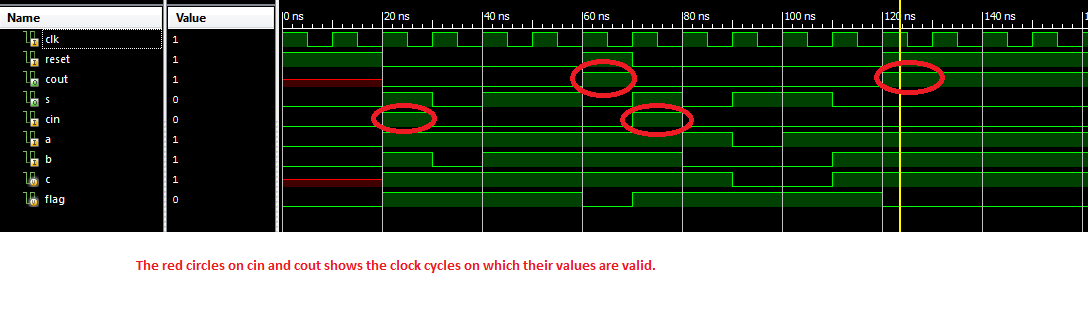

I've tried to start storing the result at index_counter - 1 since the index jumps to 1 on the first clock cycle, but then I get a fatal error in the simulation. Im trying to implement a serial adder/subtractor in VHDL, Ive done it the ripple carry way before but now Im supposed to implement the same functionality by just using one full adder cell instead of N-amount of cells so I have to shift the bits from the vectors in to the full adder/subtractor and store the result in another vector which I. The problem I have is that the counter increases to 1 right away when it enters the process so that when I try to add the vectors a = 0101 0101 and b = 1010 1010 I get y = 1111 111X and the carrys = 0000 000X. proposed a Verilog HDL coding of non-restoring division algorithm as shown in Figure-1. VHDL code for an N-bit Serial Adder with Testbench code Normally.But I obviously encounter problems since I'm probably still thinking a bit too much software programming I guess. Last time, I presented a VHDL code for a clock divider on FPGA. Full Adder Module in VHDL and Verilog Full adders are a basic building block for new digital designers. File: 4 Bit Adder / Subtractor Design using Structural Modeling Style.vhd library IEEE. Design: verilog upload - Author: Naresh Singh Dobal. The logic behind it is very easily understood, you just have a counter for the index and so on. Verilog Code For Serial Adder Subtractor Vhdl - grayjoher. I'm trying to implement a serial adder/subtractor in VHDL, I've done it the ripple carry way before but now I'm supposed to implement the same functionality by just using one full adder cell instead of N-amount of cells so I have to shift the bits from the vectors in to the full adder/subtractor and store the result in another vector which I just shift the index for as well.

0 kommentar(er)

0 kommentar(er)